WP3 Simulation and modeling

In addition to the necessary technological developments in WP1 and WP2, AI circuits can only be successfully and widely used if appropriate design and simulation tools are established. WP3 thus forms a bridge to the more application-oriented WPs 4-6 and DP. Since not all physical details of memristive devices are yet understood, the development of physical simulation models is still in its infancy. These models contribute to the physical understanding of memristive device technologies and help optimize them. Simplified compact models that allow for fast simulation time are also needed to develop memristive AI circuits. To optimize the technology in context with application in AI circuits, higher-order design and simulation tools are also needed that allow rapid estimation of parameters such as area, energy, and performance. Therefore, this WP pursues three goals in three sub-work packages.

· Development of models for the memristive devices (WP 3.1)

· Development of models for memristive matrices and 3D interconnects (WP 3.2)

· Develop higher-level design and simulation tools for AI circuits (WP 3.3).

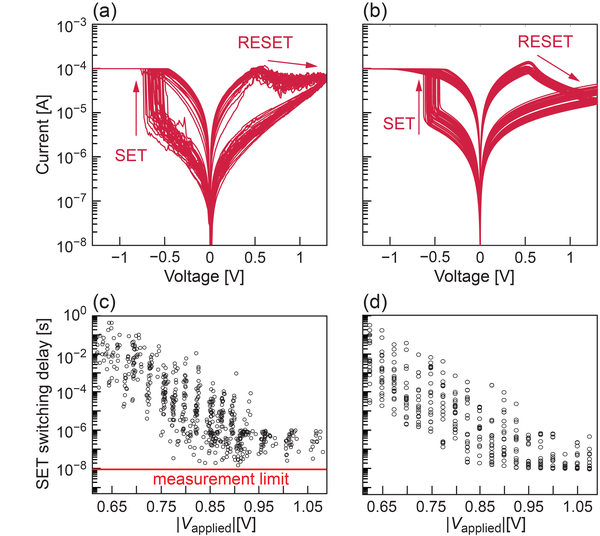

In WP 3.1 physical models for the memristive devices produced in Neurotec II will be developed. For this purpose, different approaches are pursued starting with transport calculations on the atomic scale up to compact models that can be used in circuit simulators. These compact models can then be used in AP4-6 and DP for circuit design. All compact models are published under the name Jülich-Aachen ReRAM Tools (JART) on our website www.emrl.de/jart.html. For filamentary VCM cells, compact models were developed in Neurotec I, which represent cycling variability and device variability (see Figure 1).

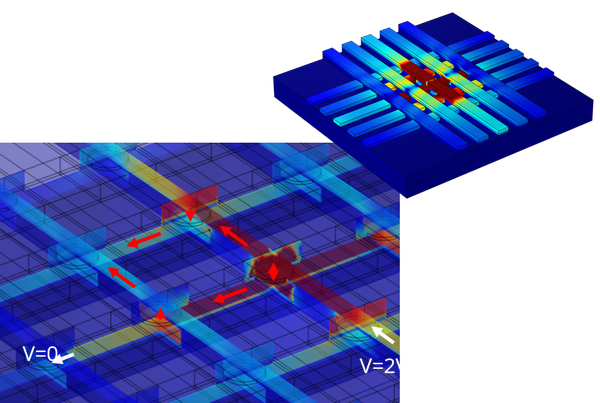

In WP3.2, the interaction of memristive components with each other is investigated. Especially when integrated into matrices with high memory density, the individual memory cells are built close together. This can lead to thermal crosstalk (see Figure 2). This crosstalk must be taken into account in matrix models. A pure consideration as single cells is no longer possible for high storage densities. The simulations also enable a design of matrices that prevents thermal crosstalk. The development of design rules for matrices and the development of models for whole matrices considering the interaction of the different cells are the main goals of this work package.

For an evaluation of the novel computing concept based on memristive memory devices, higher-level system-level tools must also be developed. Only by comparison on system level the novel computing concepts can be compared with conventional purely CMOS-based concepts. In Neurotec I, it has already been shown that an architecture based on minimizes energy consumption.