AP5 Konzepte für neuromorphe Schaltungen

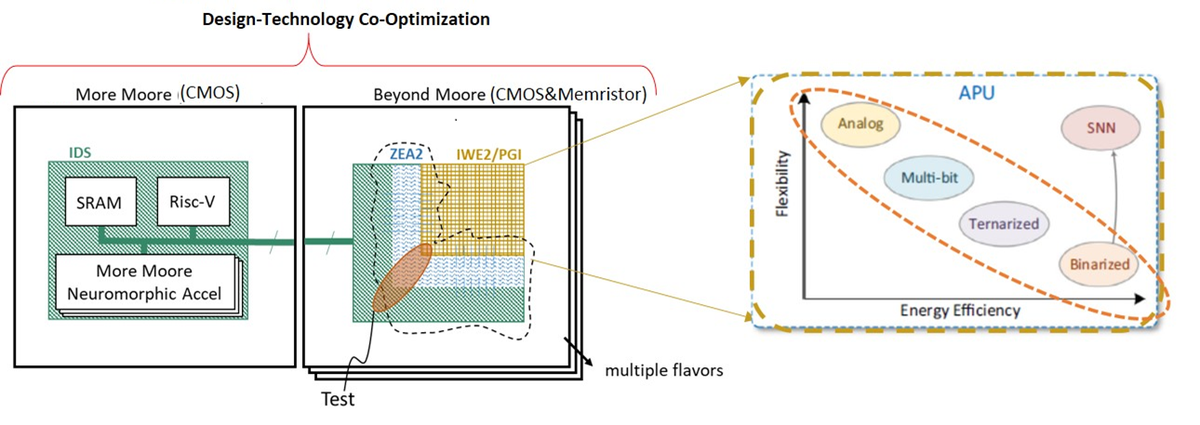

Das Arbeitspaket zielt auf die Erforschung und Entwicklung neuartiger neuromorpher Schaltungen, die sich einerseits auf hybride digital/analoge Schaltungen beziehen und eine Kombination von CMOS- und memristiver Hardware nutzen („Beyond Moore“) und andererseits auf digitaler CMOS-Hardware („More Moore“) aufbauen. Darüber hinaus soll auf einer höheren Ebene eine Entwurfs-Technologie-Ko-Optimierung (Design-Technology Co-Optimization, DTCO) unter Verwendung von Beyond-Moore- und More-Moore-Technologien ausgeführt werden.

Forschungsgebiete

Memristorbasierte Beschleuniger für analoges Rechnen-im-Speicher (Computing-In-Memory, CIM)

Entwicklung und Analyse von Memristor-Transistor-Schaltungen für Berechnungsfunktionen, einschließlich linearer Algebra-Operationen im analogen Bereich. Durchführung von Analysen auf Array-Ebene, einschließlich Themen auf Bauelemente-Ebene wie Variabilität, Analog- oder Multibit-Betrieb und Eingangs-/Ausgangskodierungen.

Memristorbasierte analoge TCAM-Blöcke

Aufbau kompakter Schaltungen mit geringerem Stromverbrauch und höherer Funktionalität für inhaltsadressierbare Speicher (Contents Addressable Memory, CAM) mit CMOS+Memristoren. Nutzung nichtflüchtiger, zweipoliger Bauelemente mit einem geringen Flächen- und Strom-Verbrauch und Erforschung geeigneter Anwendungen.

Memristorbasierte funktionale Spiking Neural Network -Bauelemente

Aufbau von lern- und anpassungsfähigen neuromorphen Spiking Neural Network (SNN)-Kernen auf dem Chip unter Verwendung von Memristoren. Einbeziehung und Nutzung von ansonsten schädlichen Effekten wie Variabilität und Nicht-Idealitäten auf Bauelemente-Ebene sowie Erforschung von Anwendungen in der räumlich-zeitlichen Verarbeitung.

Probabilistisches Computing

Entwicklung von memristor-basierten probabilistischen Blöcken, die die Stochastizität und Variabilität von memristiven Bauelementen nutzen. Beispiele hierfür sind Physical Unclonable Functions (PUFs) und True Random Number Generators (TRNGs).

Analyse neuromorpher Hardware Security

Aspekte der Hardware Security neuromorpher Systeme werden erstmals untersucht. Hierbei wird vor allem die Existenz von sogenannten „Seitenkanälen” betrachtet. Diese Kanäle erlauben es Angreifern Informationen über ein System, z.B. über die Leistungsaufnahme, zu extrahieren. In dem Arbeitspaket werden drei verschiedene Arten genauer betrachtet: Leistungs-, Zeit- und Thermische-Seitenkanäle.

System On Chip (SoC) Entwurf More Moore

Eine Validierung erfolgt in Form von Demonstratoren (D1, D2, SoC und SoC+), wobei sich die physikalischen Realisierungen in solche mit „More Moore“- und „Beyond Moore“-Technologie aufteilen.

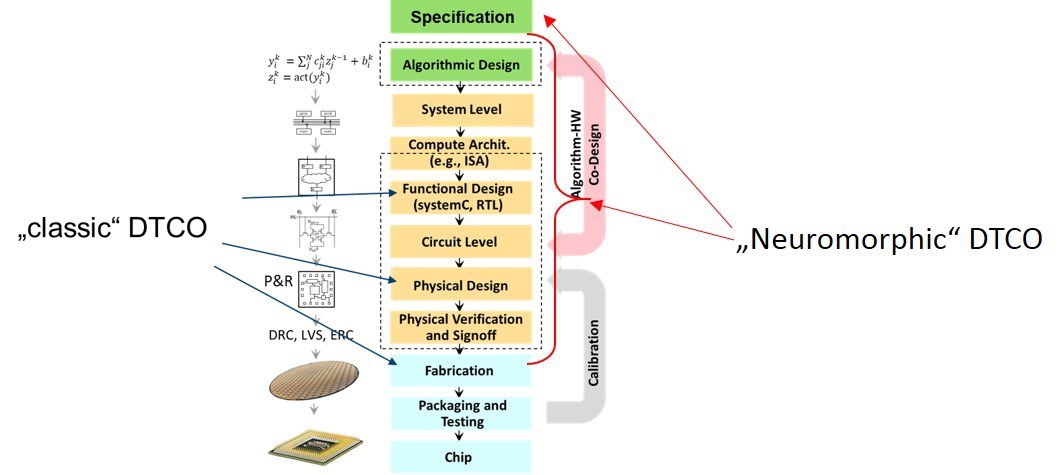

Design-Technology Co-Optimization (DTCO)

In diesem Arbeitspaket soll die Entwurfs-Technologie-Ko-Optimierung (DTCO) auf die Entwicklung neuartiger Bauelemente-Eigenschaften erweitert werden.

Während klassische DTCO nach technologischer Optimierung sucht, um den KPI des Fixed Logic Designs zu verbessern und sich auf die Schnittstelle zwischen ISA und Software konzentriert, behebt neuromorphes DTCO Anwendungsfälle und konzentriert sich auf die Qualität der Ergebnis-Metriken. Es wendet Optimierung auf allen Ebenen der Design-Hierarchie einschließlich Materialsystemen (neuartige Bauelemente) an und benötigt quantitative Modelle, um Informationen zwischen Schichten auszutauschen.

Die Evaluation der Funktionalität der memeristiven Bausteine erfolgt dabei über deren Nutzen in ausgewählten neuromorphen Funktionsblöcken.