DP Demonstratorprojekt

Schaltungen mit Memristor-Crossbar-Arrays wird bedeutendes Potential für die Realisierung neuartiger neuromorpher Rechen- und Speicherparadigmen zugemessen. Simulationen versprechen bedeutende Steigerungen in der Rechengeschwindigkeit und Energieeffizienz. Für deren Realisierung und ihre Verknüpfung mit CMOS Schaltungen existieren allerdings noch keine etablierten industriellen Prozesslinien. Diese Herausforderung wird innerhalb des Demonstratorprojektes adressiert. Die von den Forschungs- und Kooperationsprojekten generierten Forschungsergebnisse und Technologien sollen in einem Top-Down Ansatz zu einer durchgehenden Prozesslinie zusammengefasst und die Schnittstellen in Hinblick auf eine spätere industrielle Perspektive analysiert und optimiert werden („Technology Push“).

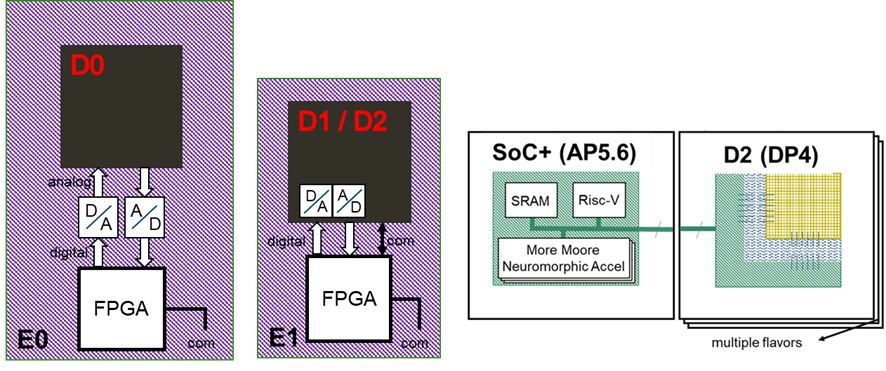

Dabei stellt die Ansteuerung der unterschiedlichen Memristorstrukturen besondere Herausforderungen an die analogen CMOS-Schaltungen, wofür innerhalb des Demonstratorprojektes möglichst generische Lösungsansätze entwickelt und verifiziert werden sollen. Der herausfordernden hardwarenahen Weiterentwicklungen der implementierten neuromorphen Paradigmen sollen die anvisierten programmierbaren Demonstratoren (TRL 4) dienen.

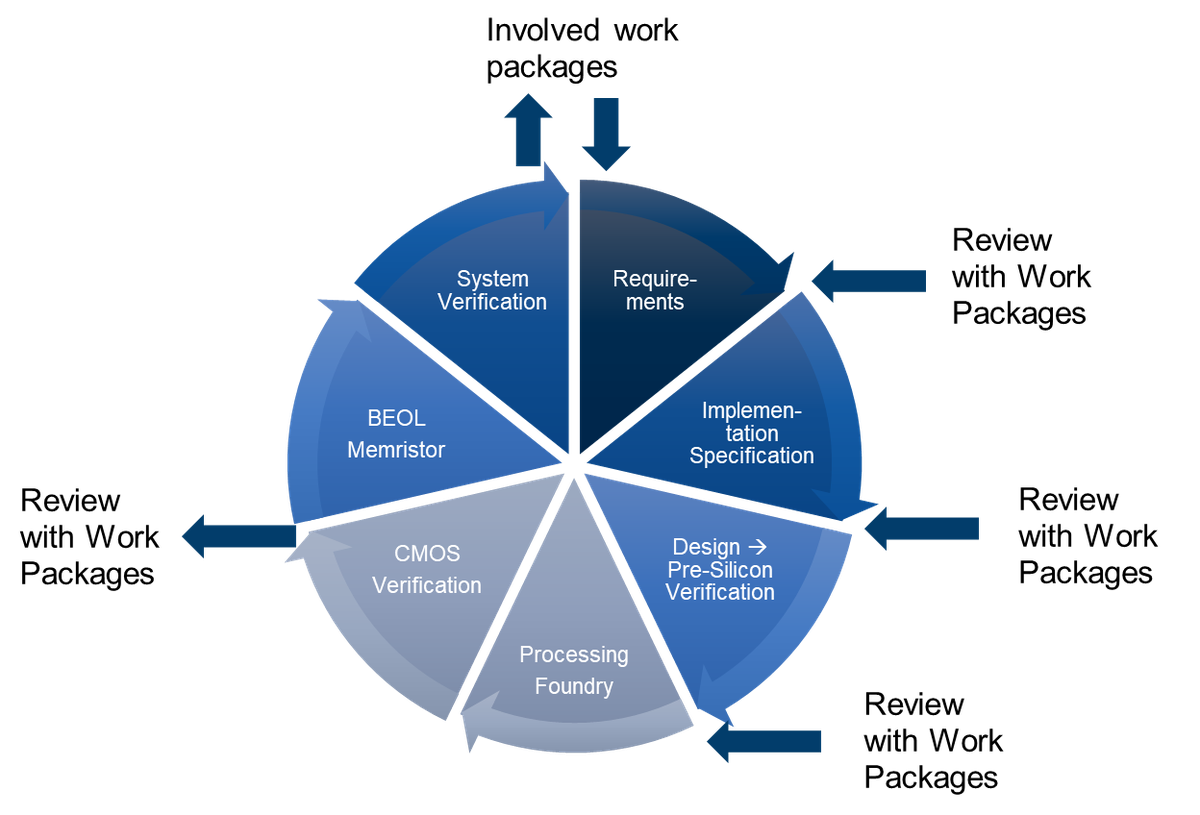

Zusätzlich soll ein Benchmarking der memristorbasierten Demonstratoren mit einer rein digitalen CMOS-Implementierung SoC+, entwickelt in einem anderen Arbeitspaket, durchgeführt werden. Hieraus sollen Erkenntnisse hinsichtlich sinnvoller Aufgabenverteilung zwischen memristorbasierten (Beyond-Moore-) und rein CMOS-basierten (More-Moore-) Ansätzen abgeleitet werden. Der Informationsfluss zwischen allen beteiligten Arbeitspaketen wird durch ein entsprechendes Reviewkonzept sichergestellt (s. Abbildung 1). Dabei erfolgt die Demonstratorentwicklung iterativ mit zunehmender Komplexität der CMOS-Schaltungen sowie Funktionalität der Memristorstrukturen (s. Abbildung 2 und 3). Der finale Demonstratorchip D2 kann sowohl über eine im Kooperationsprojekt K4 entwickelte Evaluierungsplattform als auch mittels des oben erwähnten rein digitalen Chip SoC+ betrieben werden.