DP Demonstrator project

Circuits with memristor crossbar arrays are considered to have significant potential for the realization of novel neuromorphic computing and memory paradigms. Simulations promise significant increases in computing speed and energy efficiency. However, no established industrial process lines exist yet for their realization and their interfacing with CMOS circuits. This challenge is addressed within the demonstrator project. The research results and technologies generated by the research and cooperation projects are to be combined in a top-down approach to form a continuous process line, and the interfaces are to be analyzed and optimized with a view to a later industrial perspective ("technology push").

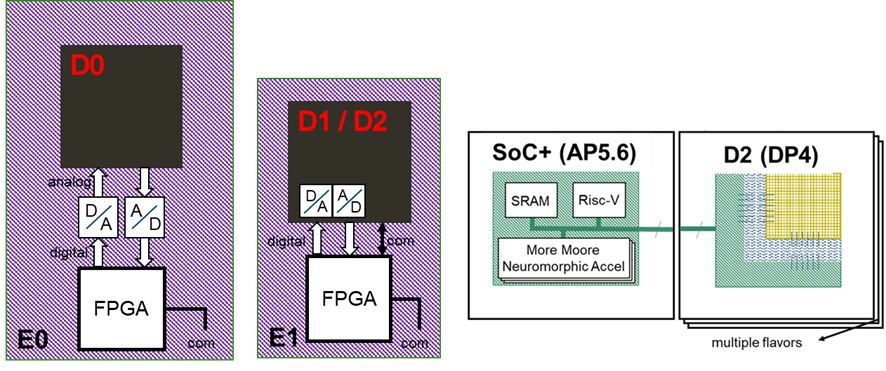

The control of the different memristor structures poses special challenges to the analog CMOS circuits, for which generic solutions are to be developed and verified within the demonstrator project. The envisaged programmable demonstrators (TRL 4) are to serve the challenging hardware-related further developments of the implemented neuromorphic paradigms.

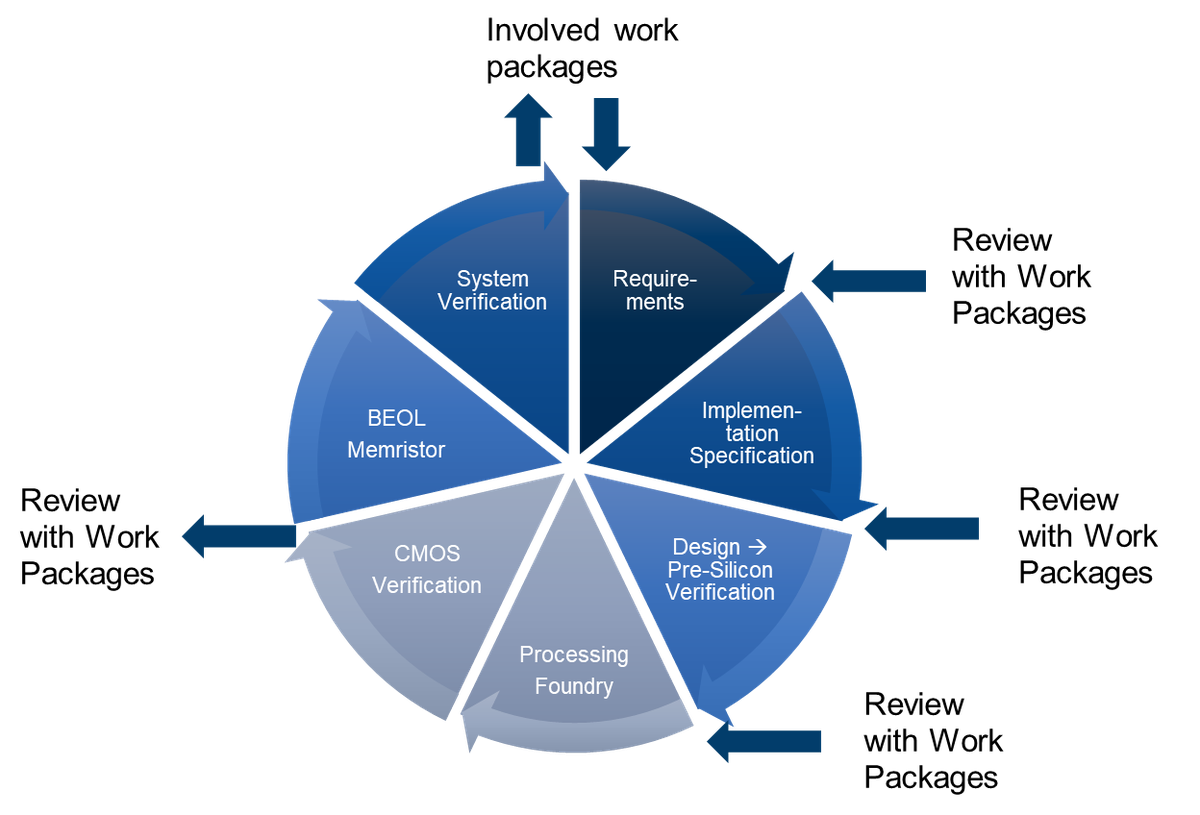

In addition, a benchmarking of the memristor-based demonstrators with a purely digital CMOS implementation SoC+, developed in another work package, will be performed. From this, findings regarding the sensible distribution of tasks between memristor-based (beyond-moore) and purely CMOS-based (more-moore) approaches will be derived. The information flow between all involved work packages is ensured by an appropriate review concept (see figure 1). The demonstrator development is iterative with increasing complexity of the CMOS circuits as well as functionality of the memristor structures (see figure 2 and 3). The final demonstrator chip D2 can be operated both via an evaluation platform developed in the K4 cooperation project and by means of the purely digital chip SoC+ mentioned above.