AP4 Mess- und Testtechnologie für neuromorphe Elektronik

Das AP4 beschäftigt sich mit allen Aspekten rund um die elektrische Charakterisierung memristiver Bauelemente und Schaltungsblöcke, die in neuromorphen Systemen Verwendung finden sollen. Um die in NEUROTEC II hergestellten Bauteile, Matrixstrukturen und Schaltungsblöcke umfassend charakterisieren zu können, wurde das AP4 bereits in der ersten Projektphase mit innovativer Messtechnik ausgestattet. Diese wird in der zweiten Projektphase in enger Zusammenarbeit mit unseren Industriepartnern aixACCT Systems sowie AMOtronics im Rahmen des Teilprojekts K3 (Link) weiterentwickelt. Unter anderem sollen hier KI-gestützte Algorithmen zur Datenanalyse direkt in die Testumgebung integriert werden.

Innerhalb des AP4 werden drei Schwerpunkte gesetzt:

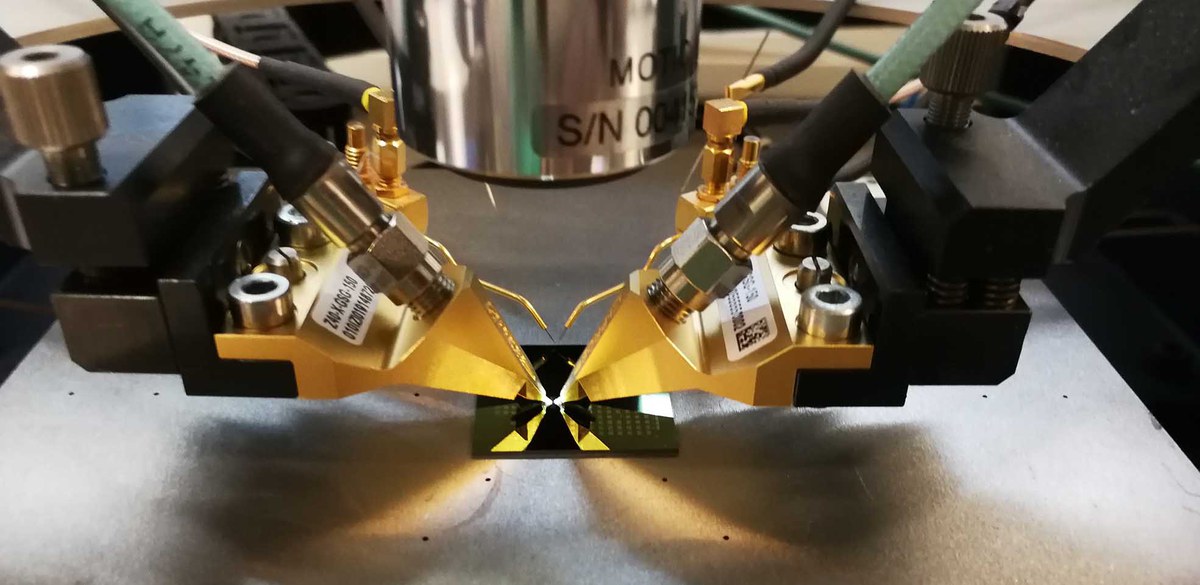

1. Ultra-Schnelle Messungen (sub-Nanosekunden)

2. Statistik und Besonderheiten von Matrixstrukturen

3. Integrierte Schaltungsblöcke und Zuverlässigkeitsanalysen

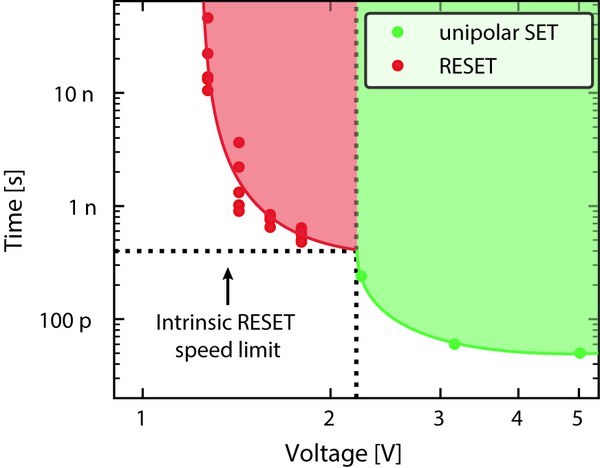

Im Bereich der ultra-schnellen Messungen wird die Schaltkinetik memristiver Bauelemente bis in den sub-Nanosekunden-Bereich untersucht, um deren Geschwindigkeitslimitierungen zu charakterisieren. Als neuer Weltrekord konnte hier bereits gezeigt werden, dass VCM (valence change mechanism) Zellen innerhalb von 50 ps eingeschaltet werden können (SET) [10.1063/5.0003840]. In der Gegenrichtung (RESET) konnte eine intrinsische Limitierung festgestellt werden. Unterhalb von 250 ps führt eine Erhöhung der RESET-Spannung nicht mehr zu kürzeren Schaltzeiten. Stattdessen tritt ein ungewollter, unipolarer SET auf [10.1021/acsaelm.1c00981].

Weitere Ziele der ultra-schnellen Charakterisierung sind die Realisierung von STP (short-term plasticity) und LTP (long-term potentiation), sowie von analogen Betriebsmodi auf der sub-Nanosekunden Zeitskala. Durch eine Erweiterung der Messtechnik soll außerdem die ultra-schnelle Charakterisierung von ECM (electrochemical migration)- und PCM (phase change mechanism) -Zellen ermöglicht werden. Weiterhin kann die hohe Geschwindigkeit für Messungen der Zyklenfestigkeit jenseits der 10^7 Schaltzyklen genutzt werden.

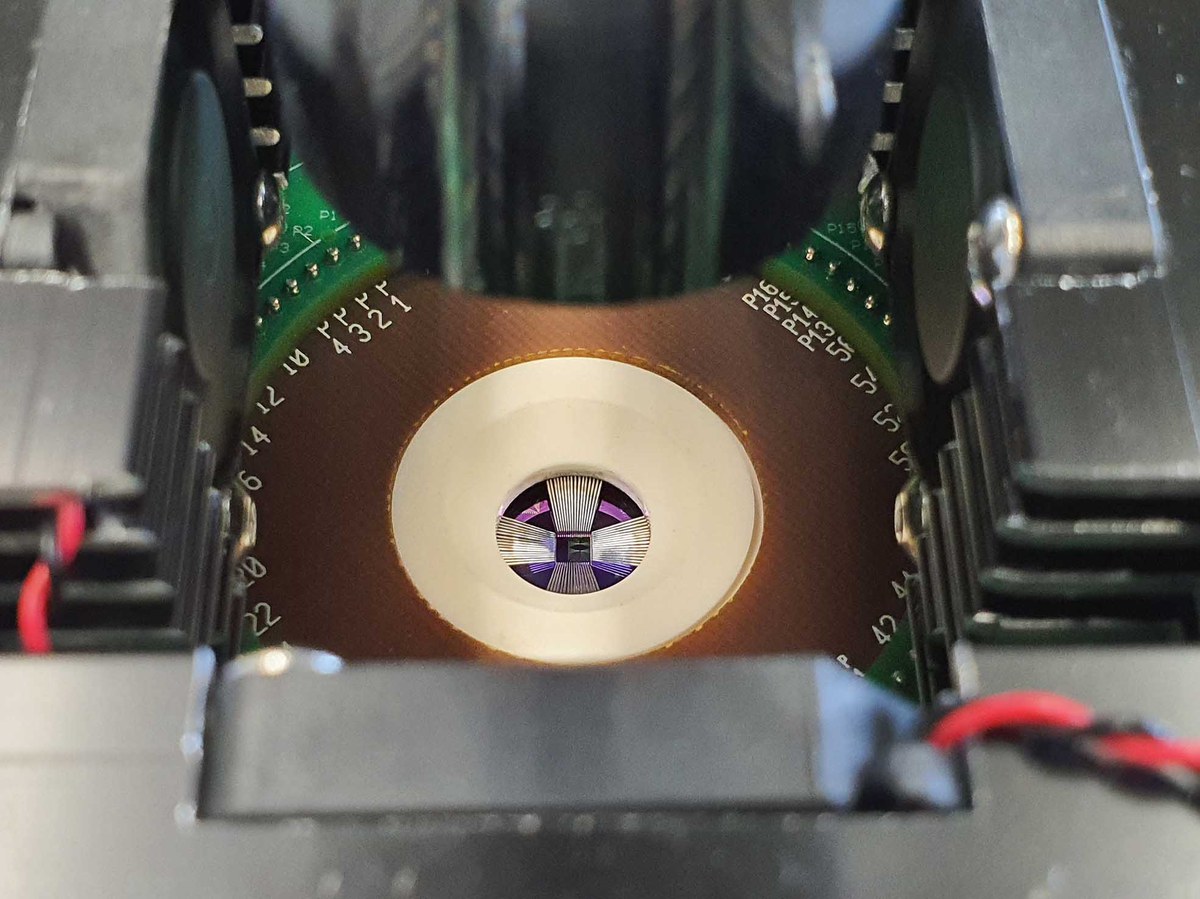

Im zweiten Themengebiet des AP4 wird die innovative Messtechnik genutzt, um Arrays memristiver Elemente zu charakterisieren. Hier konnten bereits einige Fragen der Zuverlässigkeit von VCM Zellen adressiert werden. Zum einen wurde gezeigt, dass VCM Zellen ein ionisches Rauschen im gelesenen Strom aufweisen, das auf die zufällige Bewegung von Sauerstoffleerstellen zurückzuführen ist. Werden viele Zellen in einem Array betrachtet, so führt dieses Rauschen zu einer charakteristischen Verteilung. Deren Breite wiederum limitiert die Anzahl an Zuständen, die zuverlässig unterschieden werden können [10.1109/TED.2020.3018096]. Diese Instabilität auf kurzen Zeitskalen konnte zusammen mit der Langzeitstabilität in einem konsistenten Modell durch die Bewegung von Sauerstoffleerstellen erklärt werden [10.1021/acsami.1c14667]. Außerdem wurde die Zyklenfestigkeit mit einem speziell entwickelten Algorithmus bis 10^7 Zyklen untersucht [10.1109/TED.2021.3049765].

Weitere Ziele sind die Realisierung von neuromorphen (SNN - Spiking Neural Network) und Computation-in-Memory (CIM) Funktionalitäten in memristiven Arrays. Durch den innovativen Tester werden kombinierte Hardware/Software-Lösungen möglich, um ANNs (Artificial Neural Networks) zu emulieren.

Das letzte Themengebiet des AP4 überträgt die Ergebnisse der Einzelzell- und Array-Charakterisierung in die Analyse integrierter Schaltungsblöcke und führt umfassende Zuverlässigkeitsanalysen durch. Diese betrachten auf der einen Seite fabrikationsbedingte Fehler, die zum Zeitpunkt t_0 auftreten. Das Ziel besteht darin, optimierte Fertigungsteststrategien zu entwickeln, mit denen Defekte direkt nach der Fertigung sicher detektiert werden können. Auf der anderen Seite werden Designed-for-Testability (DFT) Strategien angewendet und Fehlertoleranzansätze entwickelt, um während der Lebensdauer auftretende Fehler, direkt im Betrieb zu detektieren.

Durch eine umfassende Analyse des Fertigungsprozesses von VCM Zellen konnten bereits einige mögliche Fehlermechanismen identifiziert werden. Diese Mechanismen wurden im Zusammenhang mit möglichen, auftretenden Fehlern der Bauelemente diskutiert. Die Ergebnisse ermöglichen nun die Entwicklung präziserer Fehlermodelle und damit besserer Teststrategien [10.1007/s10836-021-05968-8].